## Contrôle final d'électronique analogique

Document autorisé : polycopié de cours uniquement - Durée : 2 h

Le but de ce problème est d'étudier une partie d'un amplificateur opérationnel compensé. La première partie concerne l'étude de l'étage d'entrée : une paire différentielle à base de transistor JFET. La seconde partie permet d'étudier le montage émetteur commun qui suit la paire différentielle. Les deux parties sont indépendantes.

## $1^{\rm \grave{e}re}$ partie

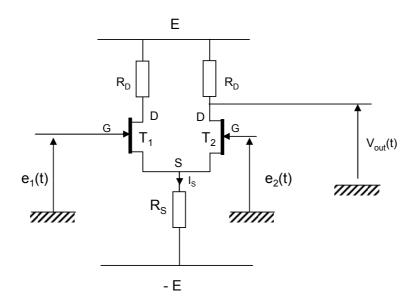

On considère le montage de la figure 1, constitué de deux transistors JFET canal N, caractérisés par une tension de seuil  $V_T = -3$  V et un courant de saturation  $I_{DSS} = 10$  mA. Les deux transistors ont les mêmes caractéristiques. On désignera par :  $V_{S1}$  et  $V_{S2}$  les tensions de source,  $V_{G1}$  et  $V_{G2}$  les tensions de grille et  $V_{D1}$  et  $V_{D2}$  les tensions de drain.

Données numériques : E = 15 V,  $R_D = 8.2 k\Omega$

Fig. 1 – Etage d'entrée d'un amplificateur opérationnel.

## 1. Etude de la polarisation.

On considère pour cette partie que les deux grilles sont reliées à la masse  $(e_1(t) = 0 \text{ et } e_2(t) = 0)$ . On veut un courant de polarisation de 1 mA dans chaque branche.

- (a) Que vaut alors le courant  $I_S$ ?

- (b) Déterminer la tension  $V_{GS}$  que l'on doit avoir sur chaque transistor JFET. (On déterminera les deux valeurs mathématiquement possibles pour la tension  $V_{GS}$  et justifiera quelle est la valeur physiquement acceptable).

- (c) Déterminer alors la potentiel  $V_S$ .

- (d) Montrer alors que la valeur  $R_S = 8.5 \text{ k}\Omega$  permet de satisfaire ce point de polarisation.

- (e) Calculer la transconductance  $g_m$  du transistor au point de polarisation considéré.

- (f) Calculer le potentiel  $V_D$ .

- 2. Etude en régime petits signaux.

On s'intéresse dans cette partie au comportement du montage en régime de petits signaux, dans la bande passante.

- (a) Déterminer le schéma petits signaux du montage complet (pour les transistors, on ne prendra pas en compte la résistance de fuite en parallèle avec les sources de courant).

- (b) Que valent les impédances d'entrées (relatives à chaque branche) du montage? Justifiez alors l'emploi de ces transistors.

On considère que la tension de sortie du montage correspond à la tension de drain du transistor 2 ( $v_{out} = v_{D2}$ ). Comme dans tout montage différentiel asymétrique, on définit le gain de mode différentiel  $A_d$  vis à vis de l'entrée différentielle  $v_{diff} = (e_1 - e_2)$  et le gain de mode commun  $A_c$  vis à vis de l'entrée commune  $v_{com} = (e_1 + e_2)/2$ .

(c) Etude du mode Commun.

On considère que  $e_1 = e_2$ .

- i. Indiquer la méthode permettant de calculer le gain de mode commun  $A_c$  à l'aide de la tension  $e_2$ .

- ii. Ecrire les relations entre  $e_1$ ,  $v_{GS1}$  et  $v_S$  d'une part (relation 1) et  $e_2$ ,  $v_{GS2}$  et  $v_S$  d'autre part (relation 2).

- iii. En déduire la relation entre  $v_{GS1}$  et  $v_{GS2}$ .

- iv. Exprimer le potentiel  $v_S$  en fonction de  $v_{GS2}$ .

- v. Exprimer alors le potentiel  $e_2$  en fonction de  $v_{GS2}$ .

- vi. Exprimer la tension  $v_{out}$  en fonction de  $v_{GS2}$ , puis de  $e_2$ .

- vii. En déduire l'expression du gain de mode commun  $A_c$ . Faire l'application numérique.

- (d) Etude du mode différentiel.

On considère que  $e_1 = -e_2$ .

- i. Indiquer la méthode permettant de calculer le gain de mode différentiel  $A_d$  à l'aide de la tension  $e_1$ .

- ii. Exprimer  $v_S$  en fonction de  $v_{GS1}$ ,  $v_{GS2}$ ,  $g_m$  et  $R_S$ .

- iii. A l'aide des relations 1 et 2 et de la question précédente, montrer que la tension  $v_S$  est nulle et en déduire la relation entre  $v_{GS1}$  et  $v_{GS2}$ .

- iv. Exprimer la tension  $v_{out}$  en fonction de  $v_{GS2}$ , puis de  $e_1$ .

- v. En déduire l'expression du gain de mode commun  $A_d$ . Faire l'application numérique.

- vi. Evaluer le taux de réjection de mode commun  $A_d/A_c$  (en dB).

- vii. Conclusion? Que faudrait-il faire pour améliorer les performances du système?

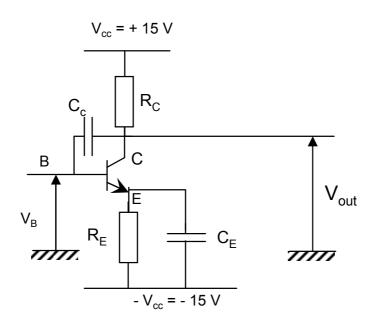

On considère dans cette partie le montage de la figure 2, qui constitue le deuxième étage d'un amplificateur opérationnel compensé. Le condensateur  $C_c$  permet de réaliser une contre-réaction et de stabiliser l'amplificateur opérationnel : l'ensemble constitue alors un système d'ordre 1. La fréquence maximale d'utilisation est plus faible, mais la marge de phase associée au système est plus importante : on perd donc en rapidité, mais on gagne en stabilité.

On supposera dans cette partie que seul le condensateur  $C_c$  intervient dans le comportement en fréquence. On supposera donc que la capacité  $C_E$  est idéale : elle est équivalente à un circuit ouvert pour les signaux constants et à un circuit fermé pour tous les autres signaux. On négligera l'influence des condensateurs internes au transistor.

On prendra les valeurs numériques suivantes :

$$R_c = 10 k\Omega$$

$$R_E = 47 k\Omega$$

$$C_c = 30 pF$$

$$\beta = 150$$

On considère que la tension  $V_B$  est la somme d'une tension constante (de polarisation)  $V_{B0} = 7 V$  et d'une tension variable  $v_B$ .

Fig. 2 – Deuxième étage d'un amplificateur opérationnel

- 1. Déterminer le point de polarisation  $(I_C, V_{CE})$ .

- 2. En déduire la valeur de la résistance dynamique base-émetteur  $r_{be}$ .

- 3. Déterminer le schéma petits signaux du montage (en prenant en compte uniquement le condensateur  $C_c$ ).

- 4. Exprimer la tension de sortie  $v_{out}$  en fonction du courant qui circule dans le collecteur et du courant qui circule dans le condensateur  $C_c$  (courant dont on choisira une convention que l'on fera figurer sur le schéma).

- 5. Exprimer le courant qui circule dans le condensateur  $C_c$  en fonction des tensions  $v_B$  et  $v_{out}$ .

6. En déduire que le gain de cet étage se met sous la forme :

$$\frac{v_{out}}{v_B} = A_v \frac{1 - j\frac{\omega}{\omega_0}}{1 + j\frac{\omega}{\omega_1}}$$

où  $A_v$  est le gain dans la bande passante. On exprimera les 3 paramètres  $A_v,\,\omega_0$  et  $\omega_1.$

- 7. Faire les applications numériques (on donnera les fréquences correspondantes). Commenter.

- 8. Tracer le diagramme de Bode en amplitude du système.

- 9. Quelle est la fréquence de coupure du système?

Fin du problème